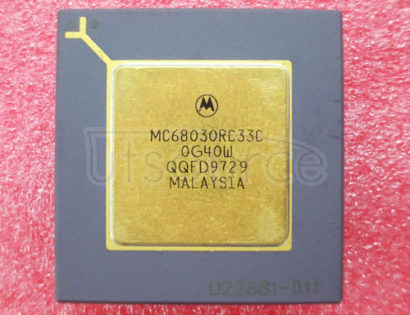

The MC68030 is a 32-bit virtual memory microprocessor that integrates the functionality of an MC68020 core with the added capabilities of an on-chip paged memory management unit(MMU) and an on-chip 256-byte data cache. Additionally, the MC68030 is enhanced with multiple internal address and data buses as well as a more versatile bus controller that can support two-clock bus accesses and one-clock burst accesses to maximize performance.The rich instruction set and addressing mode capabilities of the MC68020 have been maintained, allowing a clear migration path for M68000 systems. For detailed information on the MC68030,refer to MC68030 UM/AD,MC68030 Enhanced 32-Bit Microprocessor User's Manual.

The main features of the MC68030 are as follows:

● Object-Code Compatible with the MC68020 and Earlier M68000 Microprocessors

● Complete 32-Bit Nonmultiplexed Address and Data Buses

● 16 32-Bit General-Purpose Data and Address Registers

● Two 32-Bit Supervisor Stack Pointers and 10 Special-Purpose Control Registers

● 256-Byte Instruction Cache and 256-Byte Data Cache Can Be Accessed Simultaneously

● Paged MMU Translates Addresses in Parallel with Instruction Execution

● Two Transparent Segments Allow Untranslated Blocks To Be Defined for Systems That Transfer Large Blocks of Data to Predefined Addresses -- i.e.,Graphics Applications

● Pipelined Architecture with Increased Parallelism Allows Accesses from Internal Caches to Occur in Parallel with Bus Transfers and Instruction Execution To Be Overlapped

● Enhanced Bus Controller Supports Asynchronous Bus Cycles, (three clocks minimum),Synchronous Bus Cycles,(two clocks minimum), and Burst Data Transfers (one cock minumum), all to the Physical Address Space

● Dynamic Bus Sizing Supports 8-/16-/32-Bit Memories and Peripherals

● Complete Support for Coprocessors with the M68000 Coprocessor Interface

● Internal Status Indication for Hardware Emulation Support

● 4-Gbyte Direct Addressing Range

● Implemented in Motorola's HCMOS Technology That Allows CMOS and HMOS (High-Density NMOS) Gates To Be Combined for Maximum Speed, Low Power, and Small Die Size

● Processor Speeds Beyond 20 MHz

INTRODUCTION

The MC68030 is an integrated processor that incorporates the capabilities of the MC68020 microprocessor, the memory management structure defined by the MC68851 paged memory management unit (PMMU), data cache, an instruction cache, and an improved bus controller on one VLSI device. It maintains the 32-bit registers available with the entire M68000 Family as well as the 32-bit address and data paths, rich instruction set, versatile addressing modes, and flexible coprocessor interface provided with the MC68020.In addition, the internal operations of this integrated processor are designed to operate in parallel, allowing multiple instructions to be executed concurrently. It allows instruction execution to proceed in parallel with accesses to the internal caches, the on-chip MMU, and the bus controller.

The MC68030 fully supports the nonmultiplexed asynchronous bus of the MC68020 as well as the dynamic bus sizing mechanism that allows the processor to transfer operands to or from external devices while automatically determining device port size on a cycle-by-cycle basis. In addition to the asynchronous bus, the MC68030 also supports a fast synchronous bus for off-chip caches and fast memories. Furthermore, the MC68030 bus is capable of fetching up to four long words of data in a burst mode compatible with DRAM chips that have burst capability.Burst mode can reduce (up to 50 percent) the time necessary to fetch the four long words. The four long words are used to prefill the on-chip instruction and data caches so that the hit ratio of the caches is improved and the average access time for operand fetches is minimized.

The block diagram shown in depicts the major sections of the MC68030 and illustrates the autonomous nature of these blocks.The bus controller consists of the address and data pads, the multiplexers required to support dynamic bus sizing, and a microbus controller that schedules the bus cycles on the basis of priority.The micromachine contains the execution unit and all related control logic.Microcode control is provided by a modified two-level store of microROM and nanoROM contained in the micromachine.Programmed logic arrays (PLAs) are used to provide instruction decode and sequencing information. The instruction pipe and other individual control sections provide the secondary decode of instructions and generate the actual control signals that result in the decoding and interpretation of nanoROM and microROM information.

The instruction and data cache blocks operate independently from the rest of the machine, storing information read by the bus controller for future use with very fast access time.Each cache resides on its own address bus and data bus, allowing simultaneous access to both.Both caches are organized as a total of 64 long-word entries (256 bytes) with a line size of four long words.The data cache uses a write-through policy with programmable write allocation for cache misses.

Finally, the MMU controls the mapping of addresses for page sizes ranging from 256 bytes to 32K bytes. Mapping information stored in descriptors resides in translation tables in memory that are automatically searched by the MC68030 on demand.Recently used descriptors are maintained in a 22-entry fully associative cache called the address translation cache (ATC),allowing address translation and other MC68030 functions to occur simultaneously.Additionally, the MC68030 contains two transparent translation registers that can be used to define a one-to-one mapping for two segments ranging in size from 16 Mbytes to 2 Gbytes each.